TGV 인터포저의 디싱 제어를 위한 2-step CMP 전략

1부산대학교 대학원 기계공학부Copyright © The Korean Society for Precision Engineering

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

This paper was presented at KSPE Autumn Conference in 2023

Abstract

Chemical mechanical planarization (CMP) is an essential polishing process in semiconductor manufacturing. Advances in memory technology, including increased capacity and performance, have increased the importance of electronic packaging. In heterogeneous integration, the interposer acts as an important intermediary between the logic die and the substrate, solving numerous I/O bump problems in high-bandwidth memory (HBM) and logic chips. Traditionally, board-to-memory connections were made through wire bonding, which required additional space for wire connections and introduced latency due to extended signal transmission paths. A through-type approach has emerged as a solution that can significantly reduce waiting time and installation space by improving space efficiency and enabling vertical connections without extending wiring. Due to these new approaches, the importance of CMP is reemerging. Implementation of this important process requires precise control of the CMP dishing/protrusion of bonding surfaces. Improper selection of Cu pad dishing/protrusion can cause problems such as increased RC delay time and signal short circuit in the wiring. In this paper, we proposed a strategy to control dishing using CMP, especially for Through-glass-via (TGV).

Keywords:

Chemical mechanical planrization, Interposer, Through-glass via, Dishing키워드:

화학적 기계적 평탄화, 인터포저, 유리 관통 전극, 디싱1. 서론

반도체의 고밀도화에 대해 반세기 이상 지속되고 있던 무어의 법칙(Moore’ Law)이 한계에 직면했다. 반도체 집적 회로의 성능이 18개월마다 2배로 증가하는 무어의 법칙을 트랜지스터나 리드선 등 소자의 미세화를 통해 실현해왔다. 이러한 기술적 진보로 집적회로는 고밀도화 되었고 결과적으로 고성능화, 고속화, 저가격화로 이어졌다. 하지만, 정밀도가 올라가면서 물질을 무한히 분할하는 것은 원자의 크기라는 벽에 부딪힐 수밖에 없다.

이러한 무어의 법칙의 한계를 극복하기 위해 미세화와는 다른 방법으로 가치 높은 집적 시스템 칩을 개발하는 모어 댄 무어(More than Moore)가 고안되었다[1,2].

최근 여러 개의 메모리칩을 수직으로 적층하여 메모리 용량을 늘리고, 정보 전달 거리를 줄여 데이터 전송 속도를 향상시킨 HBM (High-bandwidth Memory)이 개발되어 HBM과 로직 칩(Logic Chip)을 나란히 붙인 2.5D 패키지가 개발되고 있다. 일반적으로 HBM 1개당 마이크로 범프(Micro Bump)의 수는 5천개 정도로 이를 기판에 직접 연결하려면 그 정도 수준의 PCB 패드를 만들어야 하고 이는 일반적 제조 공정에서는 쉽지 않은 일이다. 이처럼 진화하는 반도체 제조 환경에서 유리 인터포저(Glass Interposer)는 뛰어난 전기적 특성과 비용 효율성으로 인해 2.5D 및 3D 집적회로(IC)의 중요한 구성요소로 등장하였다[3,4].

인터포저는 제조 시 발생하는 과도한 구리층에 대한 제거가 필수적이다. 하지만 잔여 구리층을 제거할 때 발생하는 이종 재료 면에서의 연마는 Via의 디싱(Dishing)을 발생시킨다. 표면에서의 결함의 일종인 디싱은 인터커넥트 두께의 가변성을 유발하고 잠재적으로 전기적인 성능을 저하시킴으로써 반도체 장치의 무결성과 기능을 크게 훼손한다.

이 연구는 유리 인터포저 기반 반도체 장치의 신뢰성과 성능을 향상시키기 위하여 디싱 현상을 이해하고 제어하는 전략을 제시하고자 한다. 디싱의 근본 원인을 조사하고 향후 유리 인터포저 CMP 공정을 최적화하는 솔루션을 제공함으로써 반도체 제조 분야에 기여하고자 한다.

1.1 인터포저

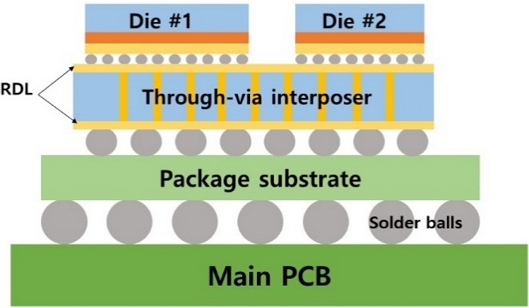

반도체 칩의 초미세화와 다양한 기능을 가진 시스템에 대한 요구가 증가함에 따라, 고집적도 및 높은 대역폭의 상호 연결에 대한 요구 또한 증가하고 있다[5]. 이러한 상황에서, 로직 칩과 메모리 칩 간의 효과적인 연결을 위한 2.5D 및 3D 패키징 기술의 핵심 요소로 인터포저가 대두되고 있다[6]. Fig. 1에서 제시된 바와 같이, 인터포저는 메모리와 칩을 서브스트레이트 사이의 중간자 역할을 하며, 특히 HBM과 로직 칩의 방대한 I/O 범프 수를 효율적으로 연결하기 위해 필수적이다. 때문에, 웨이퍼 공정을 통해 이에 대응할 수 있는 패드와 금속 배선을 만들어 HBM과 로직칩을 연결해주는 것이 인터포저이다[7].

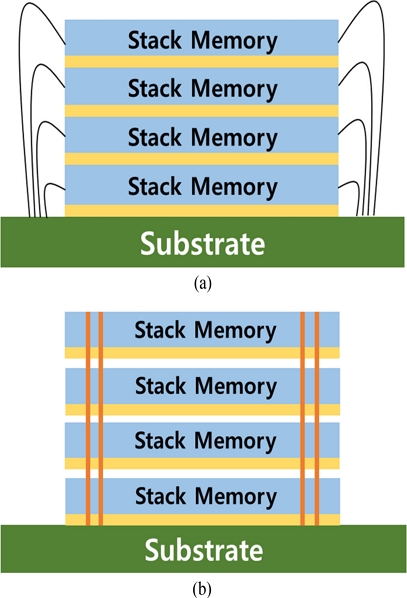

칩들을 각 기능에 맞게 사용하기 위해서는 전자가 흐르도록 외부 도선과 연결을 해야 한다. 기존에는 Fig. 2(a)에 도시된 와이어 본딩 기술을 활용하여 내부 칩과 외부를 연결하였다. 이와이어 본딩 기술은 비용 효율적이며 유연하기 때문에 널리 활용되었다[8]. 하지만, 늘어난 칩과 메모리의 양에 따라 와이어가 차지하는 공간과 전달 가능한 핀의 개수가 32개로 제한된다는 한계점이 있다. 이러한 문제점을 해결한 것이 바로 Fig. 2(b)에 도시된 Through-via 방법이다. Through-via 방법은 와이어를 바깥으로 인출할 필요가 없이 수직으로 연결하기 때문에 기존의 와이어 본딩에 비해 공간적 효율이 높다. 또한, 전기적 신호의 전달 경로가 매우 짧고, 전달할 수 있는 핀의 개수가 매우 많아 대역폭을 크게 상승시키는 장점이 있다[9].

1.2 CMP 도전과제

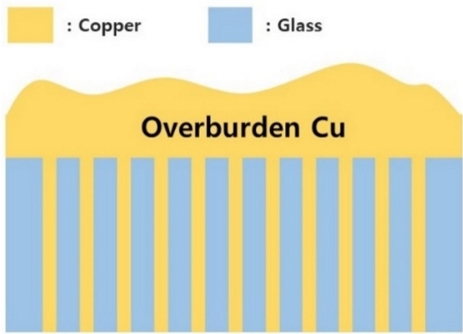

Through-via 방식을 사용한 Interposer는 다마신 기술을 통해 전도성이 높고(저항률이 낮고) 다층 배선에 폭넓게 활용될 수 있는 구리로 채워져 있다[12]. 그러나 깊은 Via에 대한 긴 도금 시간은 웨이퍼 상단에 과도한 구리층(Overburden Layer)을 형성하게 한다. (Fig. 3) 이러한 과도한 구리층은 CMP를 통해 제거될 필요가 있다. 재료 제거율(Material Removal Rate, MRR)은 CMP 공정시간에 직접적인 영향을 주는 요소이기 때문에 수율 확보 면에서 과도한 구리층을 빠르게 제거하는 것이 중요하다. 특히, CMP 공정시간의 증가는 CMP시 사용되는 소모품의 사용량 증가로 이어지게 되는데, 슬러리의 경우 고가이기 때문에, 재료 제거율이 높은 슬러리를 사용해 Bulk CMP 공정시간을 단축시킬 필요가 있다[13].

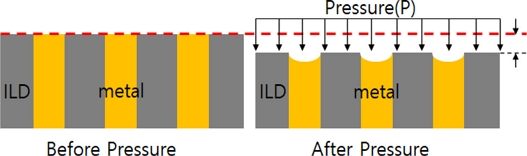

디싱이란 과다 연마 단계에서 발생하는 결함으로서 일정 패턴 영역이 움푹하게 들어간 현상을 말한다. 앞서 소개한 Bulk CMP를 진행할 때, 연마 종점은 유리 표면이 드러날 때이다. 이 지점에 도달하면 서로 물성이 다른 유리와 구리가 동시에 드러나게 된다. 연마 종점 이후의 연마로 인해 디싱이 발생하게 되는데, 그 이유는 다음과 같다.

Fig. 4에서 볼 수 있듯이, 같은 연마 압력이 작용할 때, 두 물질은 각각의 탄성계수에 비례하는 응력을 받게 되어 재료 제거율의 차이가 발생한다.

Bulk CMP에 사용된 구리의 재료 제거율이 높은 슬러리의 사용으로 인해, 연마 종점에서 구리가 더 많이 연마되어 디싱이 발생한다.

이러한 디싱 현상은 배선의 단락이나 후공정에 영향을 미친다. 특히, 패턴 형상에 직접적인 영향을 미치는 결함으로써 배선 영역에서의 단면적 감소에 따른 RC 지연 시간의 증가와 단위 면적 당 전류 밀도의 증가로 인한 Electro-migration 현상을 유발할 수 있으므로, 디싱은 Via 직경의 1/1,000 사이즈로 관리되어야 한다.

2. 이론적 배경

2.1 CMP 메커니즘

CMP는 고밀도 인터커넥트에 필수적인 표면 평탄성을 달성하게 해주는 공정으로, 표면의 화학적인 반응과 기계적인 힘을 이용하여 웨이퍼 표면의 불필요한 재료를 제거하고 평탄화 하는 과정이다. 특히, 구리를 활용한 인터커넥트 공정에서의 CMP는 더 높은 전기적 성능과 신뢰도 달성을 위해 필수적이다.

2.2 구리의 재료 제거 메커니즘

금속 CMP의 경우 슬러리와 금속의 화학 반응이 주요하다. 구리 CMP에서는 기계적인 힘뿐만 아니라, 화학적 요인 또한, 구리의 재료 제거 메커니즘에 지배적으로 작용한다. 표면에서 금속이 전자를 잃고 슬러리 속에 용해되거나 산소와 결합하여 산화막을 형성하고, 이 산화막을 연마 입자를 통해 물리적으로 제거하는 메커니즘을 포함한다[14].

3. 실험

3.1 실험 조건

실험에는 유리 웨이퍼에 100 μm 직경의 Via를 형성하고 도금을 통해 구리를 양면으로 채운 4 inch 유리 웨이퍼를 사용하였다. 연마패드와 연마장비는 각각 KPX사의 KONI 패드와 G&P Technology 사의 POLI-500 장비를 사용하였다. 1차 연마 단계에서는 연마기에 설치된 IR 센서와 Piezometer를 활용하여 실시간으로 온도와 마찰을 측정하였다. 1차 연마의 경우, 도금과정에서 생긴 잔여 구리층을 빠르게 제거하여 연마 종점에 도달하기 위해 구리에 대한 재료 제거율이 높은 슬러리를 사용하였다. 2차 연마의 경우, 일반적으로 유리 웨이퍼의 연마에서는 유리의 높은 재료 제거를 위해 Ceria 연마재를 사용하지만, 다음 단계 공정에서의 표면 거칠기와 결함에 대한 엄격한 사양에 의해 Colloidal Silica 연마재를 사용한 슬러리를 사용하였다[15]. 연마 실험에 대한 조건은 Table 1에 기술하였다. 연마 후 구리의 디싱은 Nanoscope 사의 Nanoview 로 측정되었다.

3.2 실험 결과

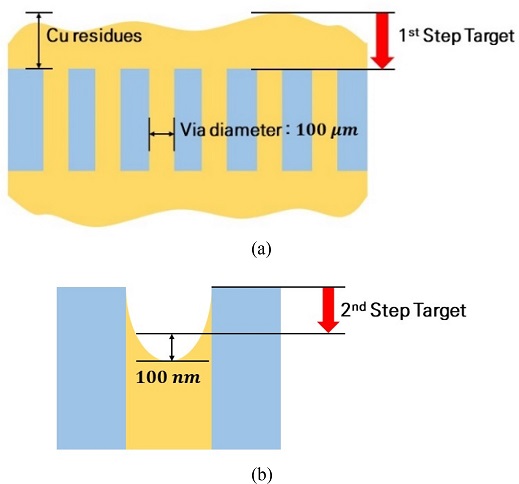

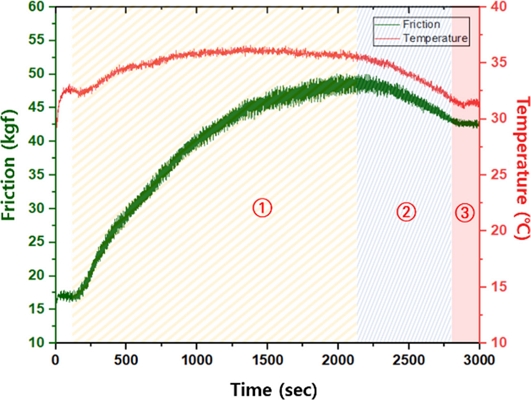

Fig. 5(a)에 도시된 것과 같이 도금 시 발생한 구리 잔여물을 빠르게 제거하기 위해 구리에 대해 높은 재료 제거율을 갖는 슬러리를 사용해 1차 CMP를 진행하였다. 상용 슬러리와 DIW, H2O 1.0 wt%를 혼합하여 실험을 진행하였다. Fig. 6 의 그래프에서 보이는 바와 같이 두드러지는 변화가 나타나는 3개의 구간을 나눌 수 있다.

- ① 온도와 마찰이 증가하는 구간

- ② 온도와 마찰이 감소하는 구간

- ③ 온도와 마찰이 일정하게 유지되는 구간

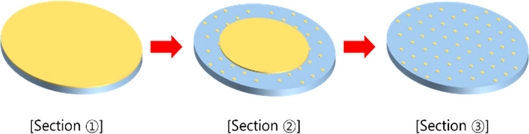

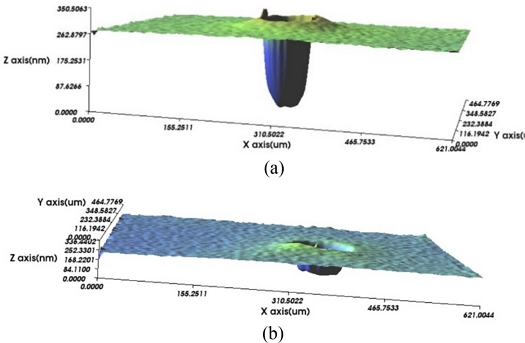

Fig. 7 과 같이 각각의 구간에서의 웨이퍼의 모습을 확인할 수 있다. 연마가 시작되면서 잔여 구리들이 슬러리와 화학적으로 반응하면서 제거가 되는데, ① 이 과정에서 마찰과 열이 증가하게 된다. 그 이후, ② 유리 웨이퍼의 표면이 일부 드러나게 되면서 반응할 수 있는 구리의 면적이 줄어들고, 발생하는 마찰과 열은 감소하게 된다. 마지막으로, ③ 모든 유리 표면이 드러나면 마찰과 열이 일정하게 유지되는 것을 확인할 수 있다. 전체 연마시간의 약 5% 정도의 시간 동안 ③ 구간 연마를 진행하였다. 3D 광학현미경을 통해 구리 부분에 발생한 디싱의 양을 측정하였다. 측정은 웨이퍼의 중심부를 기준으로 진행하였고, Fig. 8의 3차원 프로파일에서 보이는 것과 같이 구리 부분이 움푹 파인 형상을 나타내며, 5면의 웨이퍼를 측정한 결과는 Table 2에 기술하였다. 각각의 웨이퍼 면에 남아 있는 잔여 구리의 두께가 서로 달랐기 때문에 1차 CMP이 후 발생하는 디싱의 양에는 차이가 있었으며, 그 값이 Via 크기의 1/1,000 수준인 100 nm를 충족하지 못하였다. 따라서, 본 연구에서는 2차 연마를 통한 디싱 조절 전략을 수립하였다.

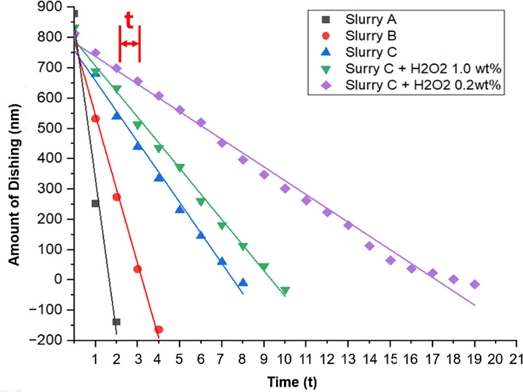

1차 CMP를 통해 발생한 디싱을 줄이기 위해서는 유리의 연마량이 구리보다 많을 필요가 있다. 따라서, 유리에 대해 선택비가 높은 슬러리인 Colloidal Silica 기반의 슬러리를 사용하였고, 이는 같은 시간 동안 많은 양의 유리 제거를 가능하게 한다. 2차 연마의 경우 빠르게 구리 잔여물을 제거하는 1차 연마와는 달리 Fig. 5(b)에 나타난 그림과 같이 원하는 수준의 디싱 양을 정밀하게 조절할 필요가 있다. 2차 연마에서 각각의 슬러리에 의한 효과를 확인하기 위해, 1차 연마 후의 웨이퍼를 약 800 nm 수준으로 과연마를 진행하였다. 2차 CMP에서는 슬러리의 연마 입자 농도와 첨가제로 사용된 과산화수소의 농도를 파라미터로 두고 각 경우에서의 디싱양 감소를 측정하였다.

Table 3에 기술된 바와 같이 12, 9, 6 wt%의 입자농도를 갖는 슬러리를 사용하였고, 그 후 입자농도 6 wt%인 슬러리에 과산화수소를 0.2, 1.0 wt%를 첨가하여 그 값을 비교하였다. 슬러리의 입자농도가 높을수록 높은 재료제거율을 보였고, 과산화수소의 농도의 증가에 따른 재료제거율은 0.0 wt%에서 0.2 wt%가 추가됨에 따라 증가하다가 1.0 wt%가 추가됨에 따라 감소하는 경향을 보였다. 이는 Table 3에 표기한 디싱 감소에 대한 계수를 통해 확인할 수 있는데, 0.2 wt%의 과산화수소가 추가되었을 때, 디싱의 감소양이 큰 폭으로 감소하였고, 1.0 wt%의 과산화수소가 추가되었을 때, 다시 디싱의 감소양이 증가한 것으로 확인할 수 있다.

일정한 시간 간격 t로 연마 후 측정된 각 슬러리 별 디싱 감소에 대한 계수들을 바탕으로 식(1)과 같은 간단한 일차식을 구성할 수 있다. 여기서 a는 Table 3에 나타낸 디싱 감소에 대한 계수를, h는 1차 연마 후 측정된 디싱의 양을 의미한다.

| h=-at+b | (1) |

각각의 슬러리에 따른 디싱의 감소량을 일정한 시간 간격 t로 연마 후 디싱의 양을 측정하였고, 각 지점의 값들을 선형 회귀하여 Fig. 9 그래프로 나타냈다. Table 3에 표기된 디싱 감소에 대한 계수는 각 슬러리 별 단위시간 t당 디싱 감소율을 나타내며, Fig. 9에 나타난 그래프의 기울기로 해석할 수 있고, 각각 509, 245, 100, 85, 45 nm 로 도출되었다.

앞선 Dishing Control CMP Process에서의 디싱 감소 계수와 식(1)을 이용하면, Bulk Cu CMP Process 후의 디싱 양인 h을 측정하여, 적절한 슬러리와 그에 따른 연마시간을 결정할 수 있다. 본 연구에서 사용된 웨이퍼의 Via 직경은 100 μm이고, 이에 따른 요구 디싱 양은 100 nm이다. 본 실험을 통해 확인한 Dishing Reduction Figs. 8(a)와 8(b)에 나타난 3차원 프로파일에서 확인할 수 있듯이, 1차 연마 후 약 258 nm의 디싱에서 85 nm 수준의 디싱으로 요구되는 디싱의 양을 충족시켰다.

4. 결론

인터포저 제조 시 Via를 채우기 위한 도금 과정에서 웨이퍼 위에 구리 잔여물이 남게 되고, 이는 CMP를 통해 제거될 필요가 있다. 또한, 잔여 구리층의 제거 과정에서 연마가 과도하게 되면 디싱이 발생하여 상호 연결의 전기적 성능에 부정적 영향을 미치게 된다. 따라서, 목표하는 디싱의 양을 달성하는 것은 매우 중요하다. 본 연구에서 진행한 두 단계의 연마는 각각의 목표를 가진다. 1차 연마의 경우 공정 시간과 공정에 드는 소모품의 비용적 부담을 덜기 위해 빠르게 연마하는 것이 필요하며, 과도하게 연마될 경우 디싱의 양이 증가하여 2차 연마의 부담을 가중시키므로, 마찰과 온도 프로파일의 실시간 감지를 통해 적절한 과연마 시간을 설정할 수 있다. 빠른 제거를 위해 구리 재료 제거율이 높은 슬러리를 사용하여, 미세한 디싱 조절에는 어려움이 있고, 이에 따라 2차 연마는 필수적이다.

따라서, 본 논문에서는 디싱 제어를 위해 다음과 같은 전략을 제시한다. 일정한 시간 간격 t로 연마 후 측정된 각 슬러리 별디싱 감소에 대한 계수들을 바탕으로 식(1)과 같은 간단한 일차식을 구성할 수 있고, 이 식과 앞선 Dishing Control CMP Process에서의 디싱 감소 계수를 이용하면, 1차 연마 후의 디싱 양인 h을 측정하여, 적절한 슬러리와 그에 따른 연마 시간을 결정할 수 있다.

Bulk Cu CMP Process 후 발생한 디싱 h와 목표 디싱양(Via 직경의 1/1,000 수준) 과의 차이가 많지 않다면, 디싱 감소 계수 a가 작은 값의 슬러리를 선정하여 연마를 진행하고, 목푯값과의 차이가 많은 경우 높은 a 값을 갖는 슬러리를 선정하여 2차 연마 시간을 단축시킬 수 있다.

Acknowledgments

이 논문은 정부(MSIP)의 재원으로 한국연구재단(NRF)의 지원을 받아 수행된 연구임(No. 20221R1A2C1095017).

REFERENCES

-

Wong, H., (2021), On the CMOS device downsizing, more moore, more than moore, and more-than-moore for more moore, Proceedings of the 2021 IEEE 32nd International Conference on Microelectronics (MIEL), 9-15.

[https://doi.org/10.1109/MIEL52794.2021.9569101]

-

Suzano, J., Abouzeid, F., Natale, G. D., Philippe, A., Roche, P., (2023), On hardware security and trust for chiplet-based 2.5D and 3D ICs: challenges and innovations, IEEE Access, 12, 29778-29794.

[https://doi.org/10.1109/ACCESS.2024.3368152]

-

Jang, J.-G., Suk, K.-L., Lee, S.-H., Park, J.-W., Jeon, G.-J., Park, J.-H., Jin, J.-G., Lee, S.-C., Kim, G.-B., Choi, J.-Y., (2020), Advanced RDL interposer PKG technology for heterogeneous integration, Proceedings of the 2020 International Wafer Level Packaging Conference (IWLPC), pp. 1-5.

[https://doi.org/10.23919/IWLPC52010.2020.9375895]

-

Liu, Z., Fu, H., Hunegnaw, S., Wang, J., Merschky, M., Magaya, T., Mieno, A., Shorey, A., Kuramochi, S., Akazawa, M., Yun, H., (2016), Electroless and electrolytic copper plating of glass interposer combined with metal oxide adhesion layer for manufacturing 3D RF devices, Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), 62-67.

[https://doi.org/10.1109/ECTC.2016.230]

-

He, H., Xue, H., Sun, Y., Liu, F., Cao, L., (2022), Design and realization of multi-channel and high-bandwidth 2.5D transmitter integrated with silicon photonic MZM, Journal of Lightwave Technology, 40(15), 5201-5215.

[https://doi.org/10.1109/JLT.2022.3175518]

-

Zhang, X., Lin, J. K., Wickramanayaka, S., Zhang, S., Weerasekera, R., Dutta, R., Chang, K. F., Chui, K.-J., Li, H. Y., Wee, D. H. S., Ding, L., Katti, G., Bhattacharya, S., Kwong, D.-L., (2015), Heterogeneous 2.5D integration on through silicon interposer, Applied Physics Reviews, 2(2), 021308.

[https://doi.org/10.1063/1.4921463]

-

Usman, A., Shah, E., Satishprasad, N. B., Chen, J., Bohlemann, S. A., Shami, S. H., Eftekhar, A. A., Adibi, A., (2017), Interposer technologies for high-performance applications, IEEE Transactions on Components, Packaging and Manufacturing Technology, 7(6), 819-828.

[https://doi.org/10.1109/TCPMT.2017.2674686]

- Wu, L., Wang, Y.-P., Kee, S. C., Wallace, B., Hsiao, C. S., Yeh, C. K., Her, T. D., Lo, R., (2000), The advent of 3-D package age, Proceedings of the 26th IEEE/CPMT International Electronics Manufacturing Technology Symposium, 102-107.

-

Gambino, J. P., Adderly, S. A., Knickerbocker, J. U., (2015), An overview of through-silicon-via technology and manufacturing challenges, Microelectronic Engineering, 135(5), 73-106.

[https://doi.org/10.1016/j.mee.2014.10.019]

-

Sukumaran, V., Chen, Q., Liu, F., Kumbhat, N., Bandyopadhyay, T., Chan, H., Min, S., Nopper, C., Sundaram, V., Tummala, R., (2010), Through-package-via formation and metallization of glass interposers, Proceedings of the 60th Electronic Components and Technology Conference (ECTC), 557-563.

[https://doi.org/10.1109/ECTC.2010.5490913]

-

Mukhopadhyay, S., Long, Y., Mudassar, B., Nair, C. S., DeProspo, B. H., Torun, H. M., Kathaperumal, M., Smet, V., Kim, D., Yalamanchili, S., Swaminathan, M., (2019), Heterogeneous integration for artificial intelligence: Challenges and opportunities, IBM Journal of Research and Development, 63(6), 8869909.

[https://doi.org/10.1147/JRD.2019.2947373]

-

Wang, S., Lee, S. R., (2011), Fast copper plating process for through silicon via (TSV) filling, Proceedings of the ASME 2011 International Mechanical Engineering Congress and Exposition, 855-863.

[https://doi.org/10.1115/IMECE2011-64782]

-

Lee, D., Lee, H., Jeong, H., (2015), The effects of a spray slurry nozzle on copper CMP for reduction in slurry consumption, Journal of Mechanical Science and Technology, 29, 5057-5062.

[https://doi.org/10.1007/s12206-015-1101-2]

-

Lee, H., Jeong, H., (2011), A wafer-scale material removal rate profile model for copper chemical mechanical planarization, International Journal of Machine Tools and Manufacture, 51(5), 395-403.

[https://doi.org/10.1016/j.ijmachtools.2011.01.007]

-

Chen, C.-C. A., Young, H.-T., Chiou, C.-H., Xue, M.-Y., Pan, C.-L., (2016), Study on CMP process of glass wafers with SiO2 based slurry for trench-glass-via interposer, Proceedings of the 2016 China Semiconductor Technology International Conference (CSTIC), 1-6.

[https://doi.org/10.1109/CSTIC.2016.7464034]

M.Sc. candidate in the Department of Mechanical Engineering, Pusan National University. His research interest is dishing control in copper CMP.

E-mail : smooth3778@pusan.ac.kr

Ph.D candidate in the Department of Mechanical Engineering, Pusan National University. His research interest is planarization modeling of copper pattern.

E-mail: oil5108@pusan.ac.kr

Ph.D candidate in the Department of Mechanical Engineering, Pusan National University. His research interest is artificial intelligence CMP system.

E-mail: jmjeong@pusan.ac.kr

Ph.D candidate in the department of Mechanical Engineering, Pusan National University. His research interest is planarization profile modeling of pattern device.

E-mail: shjeong@pusan.ac.kr

Professor in the Department of Mechanical Engineering, Pusan National University. His research fields include chemical mechanical polishing (CMP), grinding, polisher and consumable design, and post-CMP cleaning.

E-mail: hdjeong@pusan.ac.kr