즉발응답형 자발 중성자 검출기용 고이득 신호 증폭회로 설계

Copyright © The Korean Society for Precision Engineering

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

Self-Powered neutron detectors (SPND) detect current generated from interaction of neutron flux with emitter materials. They are inside a reactor in NPP (Nuclear Power Plant), and currently used to monitor the output and control the operation. Since the signal level of prompt-response SPND is very small (-nA), an analog circuit is necessary to amplify the current signal, and to convert it into voltage. This circuit needs to perform an anti-aliasing function to reduce distortion at the stage of digital conversion. In this paper, a systematic design process for high-gain amplification circuit is presented. Based on error analysis of the circuit, parameters are selected to satisfy design requirements. A third-order anti-aliasing filter is designed. A prototype circuit is built. Measured performance of the circuit confirms that the circuit satisfies all design requirements and validates the efficacy of the design to be used in practical environments.

Keywords:

Self-Powered neutron detector, Analog circuit, Instrumentation amplifier, I/V conversion, Signal compensation, Neutron flux키워드:

자발 중성자 검출기, 아날로그 회로, 계측 증폭기, 전류-전압 전환, 신호 보상, 중성자 선속1. 서론

자발 중성자 검출기(Self-Powered Neutron Detector, SPND)는 원자로 내의 중성자 선속(Neutron Flux)에 따라 자발적으로 발생하는 전류를 측정하는 장치이다. 외부전원이 필요하지 않고, 구조가 간단하여 높은 신뢰성과 긴 수명의 장점을 가지고 있다. 검출기에 사용하는 재료에 따라 전류의 생성 속도가 달라지는데, 중성자 선속 변화에 빠르게 반응하는 SPND를 즉발응답형이라 하고, 원자로 안전 감시 및 제어용으로 사용되고 있다[1].

SPND에서 발생하는 전류는 매우 미세하여, 이를 증폭하고 전압으로 변환하여야 한다. 이러한 역할을 하는 아날로그 회로는 출력 신호가 디지털 형태로 변환되는 과정에서 발생할 수 있는 왜곡을 저감하는 역할도 동시에 수행한다.

원자로 출력 감시용 로듐 기반 SPND에 대한 증폭회로는 잘 정립되어 있다[2]. 이에 비해 중성자 반응 단면적이 작아 발생 전류가 극히 미세한 즉발응답형 SPND [3]에 대한 증폭회로에 대한 연구는 매우 부족하다. 로듐 기반의 SPND는 입력 전류의 범위가 최대 10 mA의 크기이며, 디지털 변환을 위해 1,000배 정도의 증폭이 필요하다. 이에 반해 즉발응답형 SPND의 경우 발생전류가 최대 10 nA 크기이며, 증폭비는 106 범위이다. 이러한 고이득 증폭회로의 설계에 있어 오차의 원인을 파악하고, 설계 요구조건에 맞도록 회로의 형태 및 소자의 정밀도를 정하는 것이 무엇보다도 중요하다.

본 논문에서는 오차 분석에 근거하여 고이득 전류-전압 변환기 및 신호 보상 회로의 설계 과정을 제시하고, 요구조건을 만족하도록 설계를 진행하였다. 설계 결과에 따라 시제품을 제작하고, 실험을 통해 요구조건 만족 여부를 확인하였다.

2. 자발 중성자 검출기

2.1 자발 중성자 검출기 원리

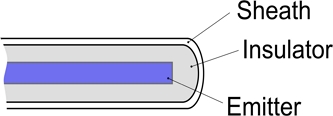

자발 중성자 검출기는 Fig. 1과 같이 방출부(Emitter), 절연체(Insulator), 피복(Sheath)으로 구성된 간단한 구조를 가지고 있다. 중성자가 방출부에 부딪히게 되면 방출부 재료의 원자핵이 동위원소로 여기되는(Excited) 핵반응이 일어나고, 동위원소는 베타 붕괴 혹은 감마 붕괴에 의해 새로운 물질로 변하면서 전자를 방출한다. 중성자 선속(Neutron Flux)에 비례하는 전자는 전류의 형태로 검출할 수 있다. 외부로부터 전원을 공급할 필요가 없으며, 신뢰성이 높고 온도나 압력에 의한 영향이 적어 원자로 내부에 설치되어 원자로의 출력을 감시하는 계측기로 널리 사용되고 있다[3].

방출부 재료로 사용되는 금속은 로듐, 바나듐, 코발트, 하프늄 등이 있다. 표준원전에서는 로듐을 주로 사용한다. 로듐은 신호 강도가 높고 수명이 긴 장점이 있지만, 중성자 선속에 대한 반응이 느려 원자로의 출력 감시용으로 사용된다. 이에 비해 코발트는 신호의 세기는 작지만, 중성자 선속에 즉각적으로 반응하는 특성을 가지고 있어 출력 감시와 제어에도 사용할 수 있다.

2.2 아날로그 증폭 회로

방출부에서 발생하는 전류는 로듐의 경우 수 mA 크기이며, 코발트에서는 수 nA 크기이다. 이를 전압의 형태로 변환하고, 크기를 증폭하여 디지털 형태의 계측기로 전달하기 위해 아날로그 증폭회로가 필요하다.

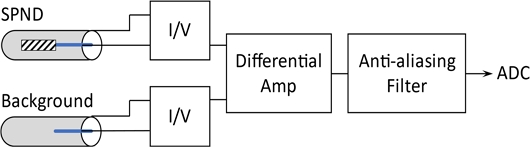

Fig. 2는 증폭 회로의 개념도로서 방출부와 피폭의 전류를 각각 전압으로 변환하고 그 차이를 증폭하는 I/V 변환부, 신호대 잡음 비를 개선하기 위해 배경 신호와의 차이를 검출하는 차동 증폭기(Differential Amplifier), 고주파 잡음으로 인한 왜곡을 저감하기 위한 Anti-Aliasing 필터 등으로 구성되어 있다.

2.3 증폭회로 설계요구조건

자발 중성자 검출기는 노내 계측기(In-Core Instrumentation)로서 온도, 압력, 수명 등 여러 가지의 요구조건을 만족해야 한다. 아날로그 증폭회로가 만족해야 할 요구조건으로 ±10 mA 범위의 입력 전류를 ±10 V 범위의 출력 전압으로 변환하며 오차가 ±1% 이내이어야 한다. 이는 로듐 기반 표준형 SPND에서 증폭회로의 출력이 디지털로 변환되기 위한 아날로그-디지털 변환기의 요구조건을 차용한 것이다. 또한, 10 Hz 이상의 주파수 성분이 필터링될 수 있도록 필터를 설계해야 한다.

증폭회로의 오차는 크게 I/V 변환 회로에 사용되는 계측 증폭기의 오차, 변환 회로의 오차, 차동 증폭기의 오차 등에 의해 결정된다. 따라서 증폭회로의 설계는 각각의 오차를 계량화하여 최소화함으로써 전체 오차에 대한 요구조건을 만족하도록 진행되어야 한다.

3. 아날로그 증폭 회로의 설계

3.1 전류-전압 변환 회로

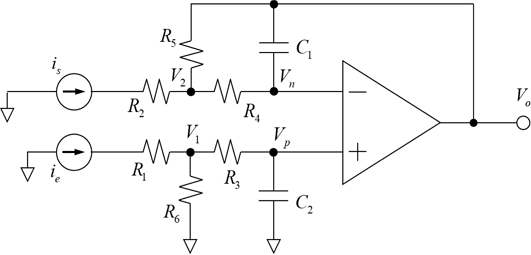

자발 중성자 검출기 신호 증폭 회로의 첫 단계는 방출부와 검출기 피복에서 발생하는 전류를 전압으로 변환하고, 증폭한 후 전압 차를 구하는 전류-전압 변환 회로이다. Fig. 3은 전류-전압 회로의 개략도로서 방출부의 전류 ie와 피복의 전류 is의차를 전압으로 변환한다. 회로의 입-출력 관계를 도출하기 위해 연산 증폭기(Operational Amplifier)의 반전 입력단 전압을 Vn, 비반전 입력단 전압을 Vp라고 하면, 연산 증폭기의 출력 전압은 식(1)로 표현할 수 있다.

| (1) |

여기서, AOL은 연산 증폭기의 개방루프 증폭비이다. 방출부 연결단과 피복연결단의 전압을 각각 V1, V2라고 하면 키르히호프 전류법칙은 다음 식(2)와 식(3)과 같다.

| (2) |

| (3) |

방출부 연결단 전압 V1과 비반전 입력 전압 Vp의 관계는 전압분배 법칙으로부터 식(4)와 같이 구할 수 있다.

| (4) |

출력 전압, 피복연결부 전압 및 반전입력단 전압의 관계는 식(5)와 같다.

| (5) |

식(1)부터 식(5)까지의 관계식을 정리하면 출력 전압 Vo와 입력 전류 간의 관계를 다음 식(6)으로 구할 수 있다.

| (6) |

여기서 궤환 인자(Feedback Factor) β는 개방루프 증폭비의 역수이다. Ge(s)와 Gs(s)는 신호 증폭과 잡음 제거를 위한 1차 저역통과 필터 형태이며 식(7)과 식(8)로 표현된다.

| (7) |

| (8) |

만일, 개방루프 증폭비가 무한대이고 저항이 모두 동일한 저항 R, 축전용량이 동일한 C라 가정하면 출력 전압은 식(9)와 같이 방출부 전류와 피복 전류의 차에 증폭비 R을 곱해 얻어지며, 차단주파수 1/2RC의 1차 저역통과 필터 특성을 지닌다.

| (9) |

3.2 계측 증폭기 오차 수지 분석

Fig. 3의 연산 증폭기로 기존의 로듐 기반 표준형 SPND의 경우 차동 증폭기를 사용한다. 그러나 즉발형 SPND는 증폭비가 표준형에 비해 1,000배 이상 커야 하기 때문에 공통모드 제거율(Common-Mode Rejection Ratio, CMRR)와 입력 임피던스가 매우 높아야 하며, 계측 증폭기가 이러한 요구조건을 만족한다. 식(6)에서 볼 수 있는 바와 같이 증폭회로의 오차는 소자의 오차와 연산 증폭기(계측 증폭기) 자체의 오차가 결정한다.

여러 가지 상용 계측 증폭기 중 고이득 증폭에 적합한 제품을 선택하기 위해 오차 수지 분석(Error Budget Analysis)를 수행하였다. 오차 수지 분석은 실제 연산 증폭기의 여러 특성이 이상적인 증폭기와 다를 때, 각각의 차이가 입출력 관계에 얼마나 영향을 주는지를 계량화하는 과정이다[4].

오차는 크게 세 가지 영역으로 분류된다. 첫 번째는 25oC 환경에서의 절대 정확도이며, 다음으로 온도가 45oC까지 상승하였을 때의 변화, 마지막으로 분해능 오차이다. 절대 정확도 오차에 기여하는 항목은 입력 오프셋 전압(Input Offset Voltage), 출력 오프셋 전압(Output Offset Voltage), 공통 모드 제거율 등이다. 예를 들어 Texas Instrument사의 INA126의 입력 오프셋 전압은 250 mV로 명시되었는데, 입력 전압의 범위가 ±10 V이면 (0.25⁄10000)×106 = 25 ppm (Parts per Million)의 오차를 계상한다.

온도가 25에서 55oC로 상승할 때의 변화 부분에 고려하는 항목으로 이득 변화, 입력 오프셋 전압 변화, 입력 오프셋 전류 변화 등이 있는데, INA126의 온도 변화에 따른 입력 오프셋 전압의 변화가 3 mV/oC이므로, (0.003⁄10000)×60×106 = 18 ppm과 같이 오차의 크기를 계량화할 수 있다. 분해능에 영향을 미치는 항목은 이득의 비선형성, 잡음의 영향 등이다. Table 1은 설계에 고려한 상용 계측 증폭기의 오차 수지 분석 결과이다. 고려한 세 제품 모두 오차의 최대 크기가 1% 수준이며, 정확성 요구조건이 만족됨을 확인할 수 있다.

3.3 전류-전압 변환 회로의 오차 분석

전류-전압 변환 회로의 오차는 계측 증폭기 자체의 오차와 변환 회로의 오차에 의해 결정된다. 앞 절의 분석을 통해 계측증폭기의 오차는 오차요구조건 내에 있음을 확인하였다. 식(9)에서 저주파 영역(s ≈ 0)의 전류 전압 관계는 식(10)으로 주어진다.

| (10) |

변환 회로의 오차는 저항의 오차에 의해 결정됨을 알 수 있다. 따라서 정밀도 1% 이하의 저항을 사용하여 요구조건을 만족할 수 있다.

3.4 Anti-Aliasing Filter (AAF)

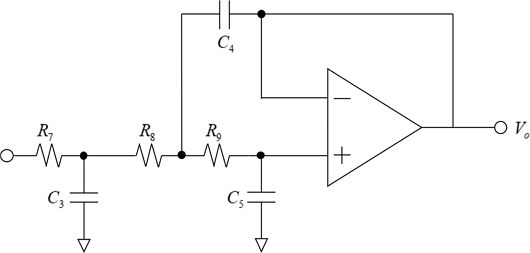

자발 중성자 검출기 신호의 주파수 대역은 10 Hz 이하이며, 그 이상의 주파수는 모두 잡음이다. 이러한 잡음은 디지털 변환 과정에서 Aliasing되어 신호를 왜곡할 수 있다. 이를 방지하고자 사용되는 필터가 Anti-Aliasing 필터로서 저역통과 필터의 특성을 가진다. Fig. 4는 본 연구에서 채택한 Anti-Aliasing 필터 구조로서, 1차 수동 RC 필터와 Sallen-Key 형태의 2차 능동 필터로 구성되어 있다[5]. 1차 수동 필터의 차단 주파수는 식(11)과 같다.

| (11) |

2차 능동필터의 차단 주파수는 식(12)로 주어진다.

| (12) |

4. 고이득 증폭 회로 설계 결과 및 성능 검증

4.1 증폭 회로 설계 결과

3장의 설계 과정을 따라 증폭회로를 설계하였다[6]. 전류-전압변환기(I/V Converter)의 증폭비를 106 로 하여 1 mA가 1 V로 변환되도록 하였다. Anti-Aliasing 필터의 차단 주파수는 7 Hz로 하였다. Table 2는 설계 결과를 정리한 표이다.

4.2 증폭 회로 성능 검증

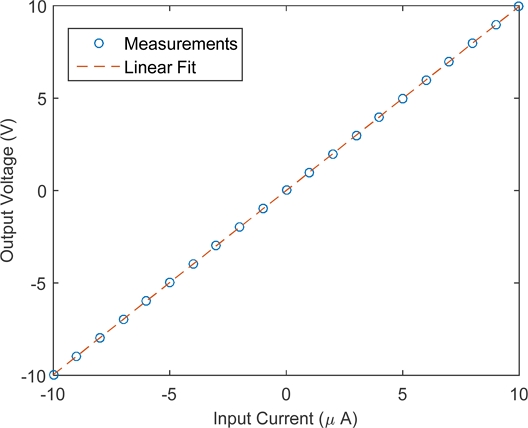

설계 결과에 따라 고이득 증폭회로의 시제품을 제작하고, 성능을 검증하였다. 전류-전압 변환 성능을 측정하기 위해 0.1 fA 분해능의 전류발생기(Keithley 2635B)를 이용하여 -10부터 10 mA까지 1 mA 간격으로 DC 전류를 생성하여 변환 회로의 입력에 연결하였다. 출력 전압은 6.5 Digit 디지털 멀티미터(Keithley 6515)를 이용하여 측정하였다. Fig. 5는 입력 전류와 출력 전류의 측정값과 측정값을 이용하여 구한 선형식을 비교하고 있다. 기울기(증폭비) 오차는 0.4%이고, 최대 선형 오차는 0.53%이어서 정확성 요구조건 1%를 만족한다.

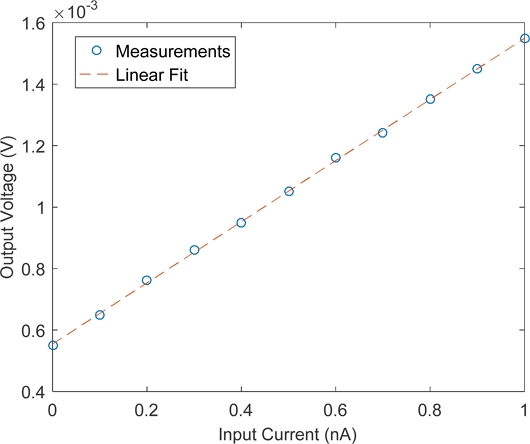

즉발응답형 SPND의 출력 전류 범위에서도 증폭회로의 성능을 검증하였다. Fig. 6은 입력 전류가 0부터 1 nA까지 0.1 nA 간격으로 변할 때 출력 전압을 측정한 결과이다. 최대 선형 오차는 8.7 nV로서 1 mV의 출력 전압 범위를 가정하면 0.87%의 오차이다. 출력 전압에 0.55 mV의 오프셋이 포함되어 있는데, 필터에 사용된 연산 증폭기의 Nulling 회로를 통해 제거할 수 있다.

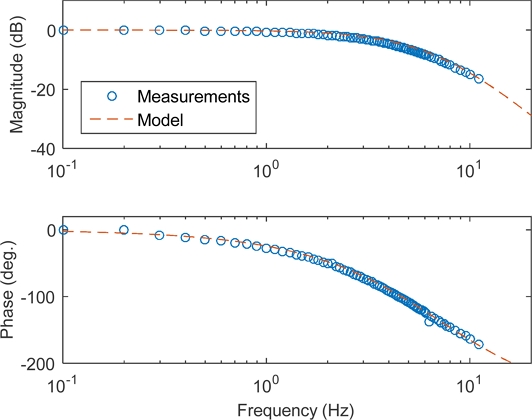

증폭회로의 동적 특성은 Anti-Aliasing 필터에 의해 좌우되며, 필터의 성능은 주파수 특성으로 확인할 수 있다. 함수 발생기를 이용하여 정현파 신호를 발생하여 AAF의 입력에 연결하고, 필터의 출력과 입력을 동시에 디지털 오실로스코프(Teradyne 4000HD)에 연결하였다. 오실로스코프의 계측 기능을 이용하여 입력과 출력의 Peak-Peak 전압과 위상차를 측정하였다. Fig. 7은 측정한 필터의 주파수 특성과 식(11) 및 식(12)로 결정되는 모델을 비교한 결과로서, 설계에서 예측한 특성이 측정값과 매우 부합함을 확인할 수 있다.

5. 결론

즉발응답형 자발 중성자 검출기(SPND)의 고이득 전류-전압변환기와 Anti-Aliasing필터 회로를 설계하였다. 요구조건을 충족하는 설계를 위해 증폭회로의 오차분석을 수행하였고, 계측 증폭기와 소자를 선정하였다. 실험을 통해 회로의 최대 선형 오차가 0.5%로 설계요구조건을 만족함을 확인하였다. 향후 잡음의 영향을 최소화하는 기판 설계를 통해 오차는 더욱 줄어들 수 있지만[7], 온도나 습도 등의 환경 변화에 대한 성능 검증이 필요할 것으로 예상된다.

NOMENCLATURE

| SPND : | Self-Powered Neutron Detector |

| CMRR : | Common-Mode Reject Ratio |

| AAF : | Anti-Aliasing Filter |

| ppm : | Parts per Million |

| ie : | Emitter Current |

| is : | Sheath Current |

| s : | Laplace Variable |

| AOL : | Open-Loop Gain of Operational Amplifier |

| β : | Feedback Factor |

Acknowledgments

이 논문은 2020년도 산업통상자원부의 재원으로 한국에너지기술평가원의 지원을 받아 연구되었음(No. 20206510100040, 고성능 노내 핵계측기 신호 측정 계통 국산화 및 즉발응답 계측 기반 기술 개발).

REFERENCES

-

Goldstein, N., Todt, W., (1979), A survey of self-powered detectors-present and future, IEEE Transactions on Nuclear Science, 26(1), 916-923.

[https://doi.org/10.1109/TNS.1979.4329746]

-

Yusuf, S. O., Wehe, D. K., (1990), Analog and digital dynamic compensation techniques for delayed self-powered neutron detectors, Nuclear Science and Engineering, 106(4), 399-408.

[https://doi.org/10.13182/NSE90-A23765]

- Todt, W. H., (1996), Characteristics of self-powered neutron detectors used in power reactors, Proceedings of a Specialists’ Meeting on In-Core Inst. and Reactor Core Assessment, NEA Nuclear Science Committee.

- Nash, E., (1999), Errors and error budget analysis in instrumentation amplifier applications, Application Note AN-539, Analog Devices.

-

Jung, W., (2005). Op Amp applications handbook. Newnes.

[https://doi.org/10.1016/B978-075067844-5/50152-1]

- Kitchin, C., Counts, L., (2006). A designer’s guide to instrumentation amplifiers. Analog Devices.

- Zumbahlen, H., (2007). Basic linear design. Analog Devices.

Ph.D. candidate in the Department of Mechatronics Engineering, Chungnam National University. His research interest is nuclear I&C.

E-mail: heejuneis@cnu.ac.kr

Professor in the Department of Mechatronics Engineering, Chungnam National University. His research interest is electro mechanical system.

E-mail: mnoh@cnu.ac.kr

Professor in the Department of Mechatronics Engineering, Chungnam National University. His research interest is Smart sensors and actuators.

E-mail: ywpark@cnu.ac.kr